سلام به همه

احساس کردم به همچین تاپیکی خیلی نیاز هست.

از این پس تمام Core هایی که خودتون مینویسید و یا از جایی میگیرید-میتونید در این تاپیک به اشتراک بزارید

فرمت قرار دادن Core ها به شکل زیر باشه که همه چیز مشخص باشه و به راحتی بشه Core مورد نظر رو پیدا کرد-از قرار دادن پست های غیر مربوط خودداری کنید و سوال ها در تاپیک های دیگه بپرسید :

نام Core

توضیحی در مورد Core

توضیح در مورد ورودی و خروجی Core

دیگه شروع کنید.

ممنونم

(((پاورقی)))

توضیح کوچکی در مورد Core:

با یک مثال توضیح میدم

یک IC رو در نظر بگیرید

مثل 7400 که 4 گیت NAND است

ما در VHDL یا Verilog این توانایی رو داریم که چنین آی سی رو بسازیم.

حالا کجا و به چه شکل؟

همان تکه کد VHDL یا Verilog که مینویسید-برای سیستم بصورت یک آی سی تفهیم میشه

حالا پایه ها کجان؟

در entity وقتی وروردی و خروجی ها رو تعریف میکنیم-در اصل در حال ایجاد پایه ها هستم

(در VHDL با entity و در Verilog در جلوی Module)

مثلا برای یک آی سی با یک گیت - پایه ها بصورت زیر تعریف میشه :

entity NAND is

port (10 : in std_logic;

9 : in std_logic;

8 : out std_logic);

وقتی برنامه تکمیل میشه و تکه کد VHDL کامپایل میشه.یک آی سی واقعی ساخته میشه.

حالا اون رو تو فولدر برنامه قرار میدید و با دستور PORT MAP ازش کپی میگیرید

ما با این کار یک Core کوچیک ساختیم

این Core میتونه متشکل از صد ها یا هزاران IC باشه.پس محدودیتی نداره.Core ها میتونن توی هم استفاده بشن.

هر قطعه دیجیتالی رو میشه به شکل Core تعریف کرد

هیچ فرقی هم نمیکنه که در کدوم ابزار پیاده سازی از جمله : ISE یا Quartus یا ... باشید.این حالت مربوط به زبان توصیف سخت افزاره

حتی این تکه کد میتونه در محیط شماتیک-کاملا شبیه سمبل یک آی سی دیده بشه و استفاده بشه

احساس کردم به همچین تاپیکی خیلی نیاز هست.

از این پس تمام Core هایی که خودتون مینویسید و یا از جایی میگیرید-میتونید در این تاپیک به اشتراک بزارید

فرمت قرار دادن Core ها به شکل زیر باشه که همه چیز مشخص باشه و به راحتی بشه Core مورد نظر رو پیدا کرد-از قرار دادن پست های غیر مربوط خودداری کنید و سوال ها در تاپیک های دیگه بپرسید :

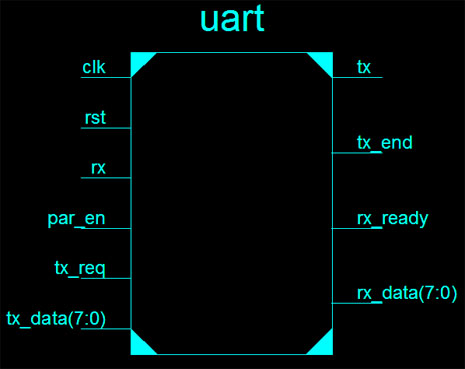

نام Core

توضیحی در مورد Core

توضیح در مورد ورودی و خروجی Core

دیگه شروع کنید.

ممنونم

(((پاورقی)))

توضیح کوچکی در مورد Core:

با یک مثال توضیح میدم

یک IC رو در نظر بگیرید

مثل 7400 که 4 گیت NAND است

ما در VHDL یا Verilog این توانایی رو داریم که چنین آی سی رو بسازیم.

حالا کجا و به چه شکل؟

همان تکه کد VHDL یا Verilog که مینویسید-برای سیستم بصورت یک آی سی تفهیم میشه

حالا پایه ها کجان؟

در entity وقتی وروردی و خروجی ها رو تعریف میکنیم-در اصل در حال ایجاد پایه ها هستم

(در VHDL با entity و در Verilog در جلوی Module)

مثلا برای یک آی سی با یک گیت - پایه ها بصورت زیر تعریف میشه :

entity NAND is

port (10 : in std_logic;

9 : in std_logic;

8 : out std_logic);

وقتی برنامه تکمیل میشه و تکه کد VHDL کامپایل میشه.یک آی سی واقعی ساخته میشه.

حالا اون رو تو فولدر برنامه قرار میدید و با دستور PORT MAP ازش کپی میگیرید

ما با این کار یک Core کوچیک ساختیم

این Core میتونه متشکل از صد ها یا هزاران IC باشه.پس محدودیتی نداره.Core ها میتونن توی هم استفاده بشن.

هر قطعه دیجیتالی رو میشه به شکل Core تعریف کرد

هیچ فرقی هم نمیکنه که در کدوم ابزار پیاده سازی از جمله : ISE یا Quartus یا ... باشید.این حالت مربوط به زبان توصیف سخت افزاره

حتی این تکه کد میتونه در محیط شماتیک-کاملا شبیه سمبل یک آی سی دیده بشه و استفاده بشه

دیدگاه