سلام

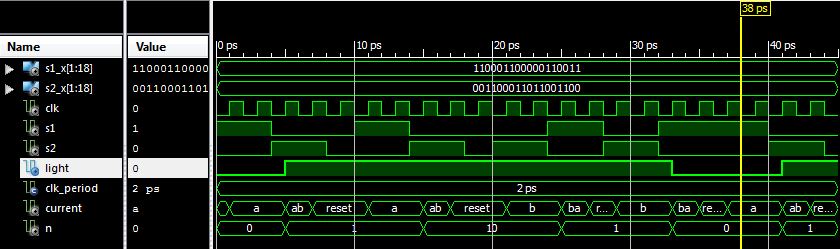

من یک برنامه نوشتم برای یک سیستم روشنایی اتوماتیک ساختمان که با استفاده ار دو سنسور و شمارش افراد وارد شده و خارج شده اما بعد از نوشتن تست بنج و شبیه سازی با isim همیشه خروجی یک میشه (لامپ روشن میمونه) برنامه ی وی اچ دی الم به صورت :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity automatic is

port(clk,s1,s2:in std_logic;

light ut std_logic

ut std_logic

);

end automatic;

architecture Behavioral of automatic is

type state is (reset,a,ab,b,ba);

signal current :state:=reset;

signal n : integer ;

begin

process(clk)

begin

if clk='1' and clk'event then

case current is

when reset =>

if (s1='1' then

then

current<=a;

end if;

if (s2='1' then

then

current<=b;

end if;

when a=>

if (s2='1' then

then

current<=ab;

n<=n+1;

end if;

when b=>

if (s1='1' then

then

current<=ba;

n<=n-1;

end if;

when others =>

current<=reset;

end case;

end if;

end process;

light<='0' when n=0 else '1';

end Behavioral;

کد تست بنچم هم اینجوریه :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY lighttestbench IS

END lighttestbench;

ARCHITECTURE behavior OF lighttestbench IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT automatic

PORT(

clk : IN std_logic;

s1 : IN std_logic;

s2 : IN std_logic;

light : OUT std_logic

);

END COMPONENT;

for all:automatic use entity work.automatic(behavioral);

SIGNAL s1_x : std_logic_VECTOR (1 to 18) :=('1','1','0',' ;0','0','1','1' ,'0','0','0','0 ','0','1','1',& #039;0','0','1','1&# 039 ;

;

signal s2_x : std_logic_VECTOR (1 to 18) :=('0','0','1',' ;1','0','0','0' ,'1','1','0','1 ','1','0','0',& #039;1','1','0','0&# 039 ;

;

--Inputs

signal clk : std_logic := '1';

signal s1 : std_logic := '0';

signal s2 : std_logic := '0';

--Outputs

signal light : std_logic:='0';

-- Clock period definitions

constant clk_period : time := 2 ps;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: automatic PORT MAP (

clk => clk,

s1 => s1,

s2 => s2,

light => light

);

-- Clock process definitions

clk_process :

process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

FOR i IN 1 to 18 LOOP

s1 <= s1_x(i);

s2 <= s2_x(i);

WAIT FOR 2 ps;

END LOOP;

end process;

END;

اشکال برنامه رو اگه می دونید بهم بگید ممنون

من یک برنامه نوشتم برای یک سیستم روشنایی اتوماتیک ساختمان که با استفاده ار دو سنسور و شمارش افراد وارد شده و خارج شده اما بعد از نوشتن تست بنج و شبیه سازی با isim همیشه خروجی یک میشه (لامپ روشن میمونه) برنامه ی وی اچ دی الم به صورت :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity automatic is

port(clk,s1,s2:in std_logic;

light

ut std_logic

ut std_logic);

end automatic;

architecture Behavioral of automatic is

type state is (reset,a,ab,b,ba);

signal current :state:=reset;

signal n : integer ;

begin

process(clk)

begin

if clk='1' and clk'event then

case current is

when reset =>

if (s1='1'

then

thencurrent<=a;

end if;

if (s2='1'

then

thencurrent<=b;

end if;

when a=>

if (s2='1'

then

then current<=ab;

n<=n+1;

end if;

when b=>

if (s1='1'

then

then current<=ba;

n<=n-1;

end if;

when others =>

current<=reset;

end case;

end if;

end process;

light<='0' when n=0 else '1';

end Behavioral;

کد تست بنچم هم اینجوریه :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY lighttestbench IS

END lighttestbench;

ARCHITECTURE behavior OF lighttestbench IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT automatic

PORT(

clk : IN std_logic;

s1 : IN std_logic;

s2 : IN std_logic;

light : OUT std_logic

);

END COMPONENT;

for all:automatic use entity work.automatic(behavioral);

SIGNAL s1_x : std_logic_VECTOR (1 to 18) :=('1','1','0',' ;0','0','1','1' ,'0','0','0','0 ','0','1','1',& #039;0','0','1','1&# 039

;

;signal s2_x : std_logic_VECTOR (1 to 18) :=('0','0','1',' ;1','0','0','0' ,'1','1','0','1 ','1','0','0',& #039;1','1','0','0&# 039

;

;--Inputs

signal clk : std_logic := '1';

signal s1 : std_logic := '0';

signal s2 : std_logic := '0';

--Outputs

signal light : std_logic:='0';

-- Clock period definitions

constant clk_period : time := 2 ps;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: automatic PORT MAP (

clk => clk,

s1 => s1,

s2 => s2,

light => light

);

-- Clock process definitions

clk_process :

process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

FOR i IN 1 to 18 LOOP

s1 <= s1_x(i);

s2 <= s2_x(i);

WAIT FOR 2 ps;

END LOOP;

end process;

END;

اشکال برنامه رو اگه می دونید بهم بگید ممنون

دیدگاه