پاسخ : طراحی چند TTL بر روی CPLD

واقعا مرسی یه دونه تشکر کمه

راضی به این همه زحمت نبودم

الان دو تا مشکل دارم یکی اینکه این آی سی XC2C64A به اصطلاح از خانواده Cool Runner II هست که حداکثر با 3.3 ولت کار میکنه ولی مدار من 5 ولت هست بنابراین از این آی سی نمیتونم استفاده بکنم.

از طرف دیگه هم آی سی XC9572 رو نتونستم اینجا پیدا بکنم

با توجه به این مقایسه بین مشخصات آی سی ها :

XILINX CPLD PRODUCTS

ظاهرا از XC9536 هم میتونم استفاده بکنم که البته از XC9572آ ضعیف تر هست. این طور نیست؟

مسئله بعدی اینه که به نظر میاد که این قسمت برنامه نویسیش یه کمی اذیتم بکنه

البته اون طوری که توی آموزشها دیدم ظاهرا کدهای آماده هم توی خود برنامه وجود داره که میشه ازشون استفاده کرد

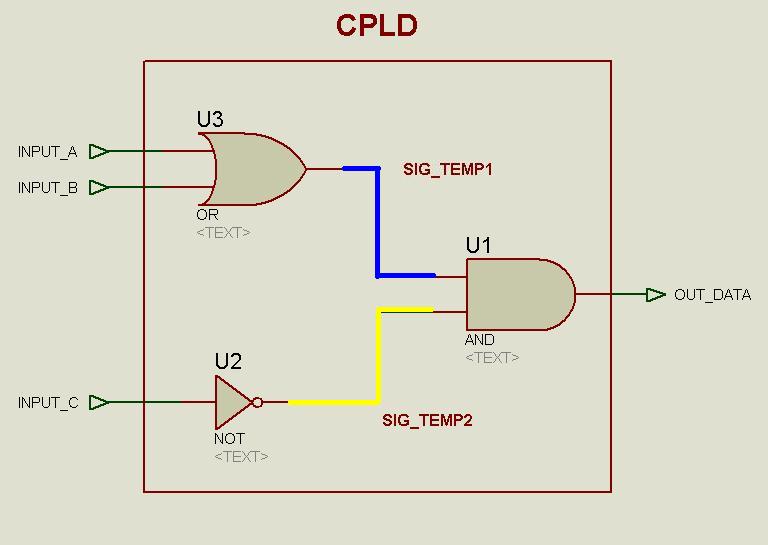

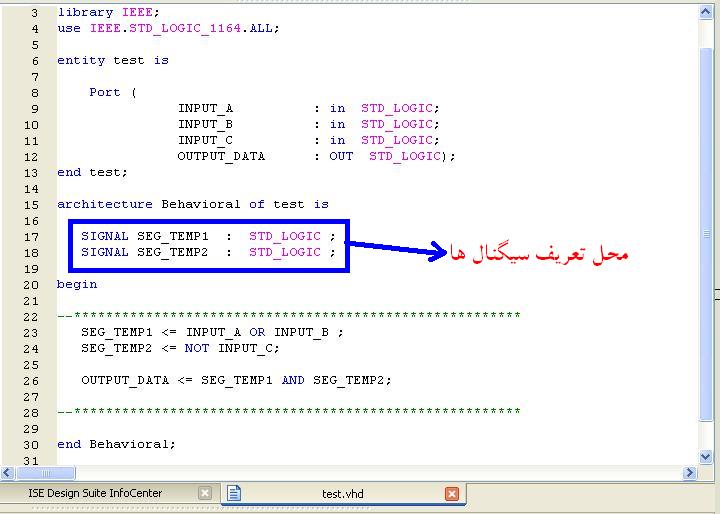

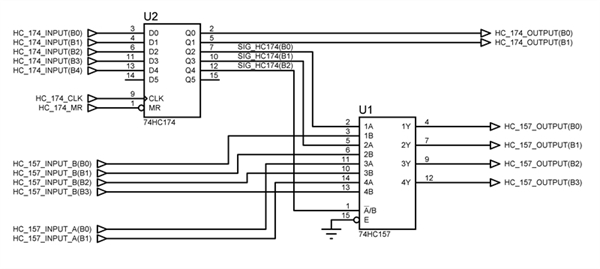

ولی اینکه چطوری میشه پایه های دو (یا چند تا TTL) رو به صورت اینترنال و با برنامه نویسی به هم دیگه ارتباط داد واقعا سخت به نظرم میاد

اگه میشه یه چند خط برنامه نمونه واسه ارتباط دو تا TTL واسم بنویس :

واقعا مرسی یه دونه تشکر کمه

راضی به این همه زحمت نبودم

الان دو تا مشکل دارم یکی اینکه این آی سی XC2C64A به اصطلاح از خانواده Cool Runner II هست که حداکثر با 3.3 ولت کار میکنه ولی مدار من 5 ولت هست بنابراین از این آی سی نمیتونم استفاده بکنم.

از طرف دیگه هم آی سی XC9572 رو نتونستم اینجا پیدا بکنم

با توجه به این مقایسه بین مشخصات آی سی ها :

XILINX CPLD PRODUCTS

ظاهرا از XC9536 هم میتونم استفاده بکنم که البته از XC9572آ ضعیف تر هست. این طور نیست؟

مسئله بعدی اینه که به نظر میاد که این قسمت برنامه نویسیش یه کمی اذیتم بکنه

البته اون طوری که توی آموزشها دیدم ظاهرا کدهای آماده هم توی خود برنامه وجود داره که میشه ازشون استفاده کرد

ولی اینکه چطوری میشه پایه های دو (یا چند تا TTL) رو به صورت اینترنال و با برنامه نویسی به هم دیگه ارتباط داد واقعا سخت به نظرم میاد

اگه میشه یه چند خط برنامه نمونه واسه ارتباط دو تا TTL واسم بنویس :

oo:

oo:

دیدگاه