عرض سلام و احترام خدمت دوستان و اساتید محترم.

بنده عملکرد یک مداری که در اون از یک تراشه FPGA استفاده شده رو بررسی میکنم که به یک قسمتی برخوردم که نتونستم اطلاعاتی در مورد اون کسب کنم.

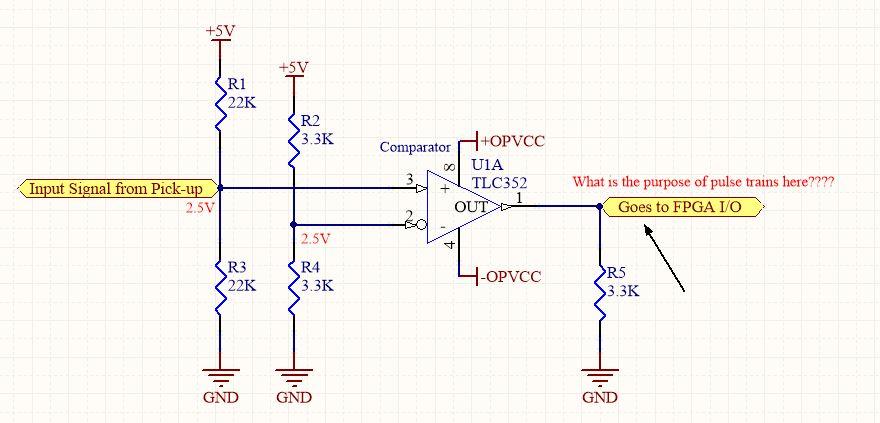

این قسمت مربوط به مقایسه یک سیگنال تقویت شده نویزی با میزان آف ست همان سیگنال هست که طبیعتا در خروجی مقایسه کننده یک قطار پالسی شبیه به نویز، ایجاد می شود که این پالسها در نهایت به ورودی FPGA فرستاده میشوند. در حالت کلی میشه حدس زد که ممکنه برای فیلترینگ دیجیتال یا فیلترینگ فاز و حذف اثر نویز استفاده شده باشه ولی اینکه توسط چه الگوریتمی و به چه منظوری میشه ازش استفاده کرد، برام سوال بزرگیه. و اینکه بعد از پردازش این سیگنال در FPGA چطور میشه خروجی این الگوریتم رو به سیگنال اصلی جهت حذف نویز تزریق کرد؟ ممنون میشم دوستان هر ایده یا نظری داشتند مطرح کنند.

بنده عملکرد یک مداری که در اون از یک تراشه FPGA استفاده شده رو بررسی میکنم که به یک قسمتی برخوردم که نتونستم اطلاعاتی در مورد اون کسب کنم.

این قسمت مربوط به مقایسه یک سیگنال تقویت شده نویزی با میزان آف ست همان سیگنال هست که طبیعتا در خروجی مقایسه کننده یک قطار پالسی شبیه به نویز، ایجاد می شود که این پالسها در نهایت به ورودی FPGA فرستاده میشوند. در حالت کلی میشه حدس زد که ممکنه برای فیلترینگ دیجیتال یا فیلترینگ فاز و حذف اثر نویز استفاده شده باشه ولی اینکه توسط چه الگوریتمی و به چه منظوری میشه ازش استفاده کرد، برام سوال بزرگیه. و اینکه بعد از پردازش این سیگنال در FPGA چطور میشه خروجی این الگوریتم رو به سیگنال اصلی جهت حذف نویز تزریق کرد؟ ممنون میشم دوستان هر ایده یا نظری داشتند مطرح کنند.